# User Manua

# **NY5+ Series**

Single-Chip 4-bit MCU with 8~32 I/O and 4-Ch Speech/MIDI

Version 1.3

Aug. 24, 2022

NYQUEST TECHNOLOGY CO. reserves the right to change this document without prior notice. Information provided by NYQUEST is believed to be accurate and reliable. However, NYQUEST makes no warranty for any errors which may appear in this document. Contact NYQUEST to obtain the latest version of device specifications before placing your orders. No responsibility is assumed by NYQUEST for any infringement of patent or other rights of third parties which may result from its use. In addition, NYQUEST products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of NYQUEST.

# **Revision History**

| Version# | Date       | Description                                    | Modified Page |

|----------|------------|------------------------------------------------|---------------|

| 1.0      | 2021/05/31 | Formal release.                                | -             |

| 1.1      | 2021/07/26 | Correct content and typos.                     | 7, 10, 16, 33 |

| 1.2      | 2022/05/27 | Add NY5Q026A, NY5Q046A, NY5Q080A, and NY5Q160A | 7, 8          |

| 1.3      | 2022/08/24 | Modify the frequency of IR Carrier             | 21            |

# **Table of Contents**

| Chapter 1. Introduction                     | b  |

|---------------------------------------------|----|

| 1.1 General Description                     | 6  |

| 1.2 Features                                | 6  |

| 1.3 OTP Product List                        | 7  |

| 1.4 Block Diagram                           | 7  |

| 1.5 Pad Description                         |    |

| 1.6 Electrical Characteristics              |    |

| 1.6.1 Absolute Maximum Rating               |    |

| 1.6.2 DC Characteristics (Preliminary)      |    |

| Chapter 2. Hardware Architecture            |    |

| 2.1 Overview                                |    |

|                                             |    |

| 2.1.1 Function Block Diagram                |    |

| 2.1.2 Hardware Summary Table                |    |

|                                             |    |

| 2.3 System Reset                            |    |

| 2.3.1 Power-On Reset (POR)                  |    |

| 2.3.2 Low Voltage Reset (LVR)               |    |

| 2.3.3 Watch-Dog Timer Reset (WDTR)          |    |

| 2.3.4 IO Port External Reset                |    |

| 2.4 Address Pointer                         |    |

| 2.4.1 Program Counter (PC)                  |    |

| 2.4.2 Stack (STK)                           |    |

| 2.4.3 Multi-function Register Pointer (RPT) |    |

| 2.5 Arithmetic Logic Unit (ALU)             |    |

| 2.5.1 ALU Instruction Summary               |    |

| 2.5.2 ALU Related Status Flag               |    |

| 2.6 Memory Organization                     |    |

| 2.6.1 ROM                                   |    |

| 2.6.2 RAM                                   |    |

| 2.6.3 Memory Register                       |    |

| 2.6.4 System Register                       |    |

| 2.6.5 Register without Memory Allocation    |    |

| 2.7 IO Ports                                |    |

| 2.7.1 Pull-High Input Mode                  | 20 |

| 2.7.2 Floating Input Mode                   |    |

| - ·                                         |    |

|    | 2.7.3 Output Mode                            | 21 |

|----|----------------------------------------------|----|

|    | 2.8 Infrared Transmitter                     | 21 |

|    | 2.9 PWM-IO Generator                         | 22 |

|    | 2.10 Interrupt Generator                     | 22 |

|    | 2.11 Audio Synthesizer Structure             | 22 |

|    | 2.11.1 Audio Output                          |    |

|    | 2.11.2 Volume Control                        |    |

|    | 2.12 Low Voltage Detector (LVD)              |    |

| Cł | hapter 3. System Control                     | 24 |

|    | 3.1 Introduction                             |    |

|    | 3.1.1 System Register Address Map            |    |

|    | 3.1.2 Memory Register Address Map            |    |

|    | 3.1.3 Register without Memory Allocation Map |    |

|    | 3.2 RPT                                      |    |

|    | 3.3 ROD                                      |    |

|    | 3.4 RAM Control Register                     | 28 |

|    | 3.4.1 XMD                                    |    |

|    | 3.5 I/O Ports Register                       |    |

|    | 3.6 INT                                      |    |

|    | 3.6.1 System Base Timer Polling              |    |

|    | 3.6.2 Interrupt Source                       |    |

|    | 3.6.3 TOF source                             |    |

|    | 3.6.4 Flag Clear                             | 29 |

|    | 3.7 Audio Control Register                   | 30 |

|    | 3.7.1 VOL                                    | 30 |

|    | 3.7.2 PFLG                                   | 30 |

|    | 3.7.3 MIX                                    | 30 |

|    | 3.7.4 AUD                                    | 30 |

|    | 3.7.5 CH#                                    | 31 |

|    | 3.7.6 TCSx                                   | 31 |

|    | 3.7.8 TMx                                    |    |

|    | 3.7.9 ENVx                                   |    |

|    | 3.8 Power Saving Mode                        | 32 |

|    | 3.8.1 Halt Mode                              | 32 |

|    | 3.8.2 Slow Mode                              |    |

|    | 3.8.3 RC Slow Mode                           | 33 |

| Cł | hapter 4. Audio Playback                     | 34 |

|    | 4.1 Introduction                             | 34 |

|    | 4.2 Speech Playback                          | 34 |

| 4.2.1 Speech Playing Procedure | 34 |

|--------------------------------|----|

| 4.2.2 Speech Data              | 32 |

| 4.2.3 Quick-IO                 | 32 |

| 4.3 MIDI Control               | 35 |

| 4.3.1 MIDI Playing Procedure   |    |

| Chapter 5. Instruction Set     | 36 |

| 5.1 Instruction Table          | 36 |

| 5.2 Instruction Descriptions   | 38 |

| 5.2.1 Arithmetic Instructions  |    |

| 5.2.2 Conditional Instructions |    |

| 5.2.3 Audio Instructions       | 44 |

| 5.2.4 Other Instructions       | 46 |

# **Chapter 1. Introduction**

### 1.1 General Description

The NY5+ series IC is a powerful 4-bit micro-controller based sound processor. There are 4 channels that are configured as speech or MIDI, and all of them can be auto-played back simultaneously. By using the high fidelity ADPCM speech synthesis algorithm, it can produce outstanding quality voices. Wide range sampling rate up to 44.1kHz and different volume level are supported. It is also equipped two kinds of audio outputs with fine resolution, including a current D/A converter and a PWM direct-drive. The RISC MCU architecture is very easy to program and control, various applications can be easily implemented. There are 43 instructions, and most of them are executed in single cycle. Furthermore, in addition to the HALT mode (sleep mode), it offers the SLOW mode to minimize power dissipation.

### 1.2 Features

- Wide operating voltage range: 2.0V to 5.5V.

- 4-bit RISC type micro-controller with 43 instructions.

- 4Mx10-bit ROM maximum, program and voice data share the same ROM space.

- 248x4-bit RAM maximum, indirect RAM addressing mode is supported.

- 1MHz or 2MHz instruction frequency (2MHz is required for over 2-ch speech or MIDI).

- SLOW mode to operate at low power consumption.

- HALT mode to save power, less than 1uA@3V standby current.

- Built-in RC oscillation is accurate with +/- 0.5% frequency deviation.

- Low voltage reset (LVR=1.8V), watch-dog reset and I/O port reset are all supported to protect the system.

- Single interrupt entrance with an independent stack, multiple interrupt sources.

- Up to 32 flexible Bi-direction I/Os. Each I/O direction is independently controlled by individual register bit.

- Shared pins to provide IR carrier and external reset feature. (Mask option)

- Selection of IR carrier frequency and data high/low IR output is supported.

- Multiple groups of 4-ch PWM-IO share a group of time, each channel has 8-bit resolution

- NY5+ series are all 4 channels and can play simultaneously; each channel can be arbitrarily assigned as speech or MIDI channel based on the product spec.

- New high fidelity ADPCM speech synthesis algorithm.

- New high fidelity mixed ADPCM or PCM speech synthesis algorithm and ADSR with 256-step envelope for MIDI synthesis.

- High quality 12-bit D/A converter or 12-bit PWM driver.

- Support 3 levels Normal, Large, Ultra PWM current output.

- 16-level digital volume control for synthetic Speech/MIDI.

- Quick-IO control supported.

- Low Voltage Detector (LVD) is built-in for monitoring the status of power and protect malfunction if unstable power is given.

### 1.3 OTP Product List

| IC Type  | Time* (sec) | ROM (bits) | RAM (bits) | I/O | PWM-IO | Channel | DAC |

|----------|-------------|------------|------------|-----|--------|---------|-----|

| NY5Q020A | 18.3        | 48K x 10   | 248 x 4    | 8   |        | 4       | Y   |

| NY5Q026A | 25          | 64K x 10   | 248 x 4    | 4   |        | 4       | Y   |

| NY5Q040A | 38.3        | 96K x 10   | 248 x 4    | 8   |        | 4       | Y   |

| NY5Q046A | 45          | 112K x 10  | 248 x 4    | 12  | 8      | 4       | Y   |

| NY5Q060A | 58.3        | 144K x 10  | 248 x 4    | 16  | 8      | 4       | Υ   |

| NY5Q080A | 78.3        | 192K x 10  | 248 x 4    | 12  | 8      | 4       | Y   |

| NY5Q092A | 91.6        | 224K x10   | 248 x 4    | 16  | 8      | 4       | Y   |

| NY5Q160A | 158.3       | 384K x 10  | 248 x 4    | 12  | 8      | 4       | Υ   |

| NY5Q172A | 171.6       | 416K x 10  | 248 x 4    | 16  | 8      | 4       | Y   |

| NY5Q342A | 345         | 832K x 10  | 248 x 4    | 20  | 8      | 4       | Y   |

<sup>\*</sup> The voice duration is calculated at 6 KHz by 4-bit ADPCM algorithm.

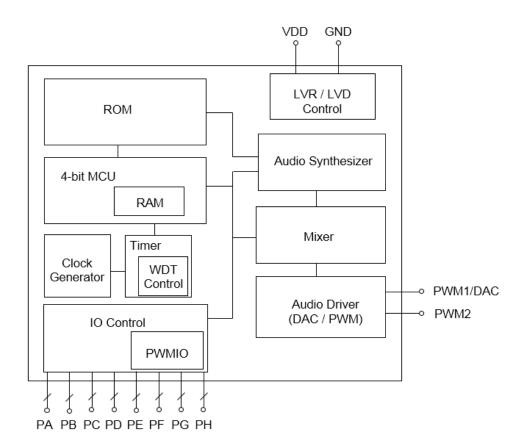

# 1.4 Block Diagram

### 1.5 Pad Description

| Pin      | ATTR. | Description               |

|----------|-------|---------------------------|

| VDD#     | Power | Positive power            |

| GND#     | Power | Negative power            |

| PWM1/DAC | 0     | PWM1 output or DAC output |

| PWM2     | 0     | PWM2 output               |

| PA0~3    | I/O   | Bit 0~3 for Port A        |

| PB0~3    | I/O   | Bit 0~3 for Port B        |

| PC0~3    | I/O   | Bit 0~3 for Port C        |

| PD0~3    | I/O   | Bit 0~3 for Port D        |

| PE0~3    | I/O   | Bit 0~3 for Port E        |

| PF0~3    | 1/0   | Bit 0~3 for Port F        |

| PG0~3    | 1/0   | Bit 0~3 for Port G        |

| PH0~3    | 1/0   | Bit 0~3 for Port H        |

<sup>\* (4</sup> I/O) NY5Q026A: PB0, PA1, PA2, PA3

### 1.6 Electrical Characteristics

The following lists the electrical characteristics of the NY5+ EV chip. All the product's properties must refer to each part's datasheet.

### 1.6.1 Absolute Maximum Rating

| Symbol    | Parameter             | Rated Value        | Unit |

|-----------|-----------------------|--------------------|------|

| VDD - VSS | Supply voltage        | -0.5 ~ +6.0        | V    |

| Vin       | Input voltage         | Vss-0.3V ~ VDD+0.3 | V    |

| Тор       | Operating Temperature | 0 ~ +70            | °C   |

| Tst       | Storage Temperature   | -25 ~ +85          | °C   |

<sup>\* (8</sup> I/O) NY5Q020A \ NY5Q040A : PA0~3, PB0~3

<sup>\* (12</sup> I/O) NY5Q046A · NY5Q080A · NY5Q160A : PA0~3, PB0~3, PD0~3

<sup>\* (16</sup> I/O) NY5Q060A · NY5Q092A · NY5Q172A : PA0~3, PB0~3, PC0~3, PD0~3

<sup>\* (20</sup> I/O) NY5Q342A: PA0~3, PB0~3, PC0~3, PD0~3, PE0~3

# 1.6.2 DC Characteristics (Preliminary)

| Symbol           | Parameter                                                              |                        | VDD      | Min. | Тур.       | Max. | Unit | Condition                                      |

|------------------|------------------------------------------------------------------------|------------------------|----------|------|------------|------|------|------------------------------------------------|

| VDD              | Operating voltage                                                      |                        |          | 2.0  | 3          | 5.5  | V    | 1MHz & 2MHz                                    |

| lsb              |                                                                        | Halt<br>mode           | 3<br>4.5 |      |            | 2    | uA   | Sleep, no load<br>with on board Flash          |

| İsi              | Supply                                                                 | Slow<br>mode           | 3<br>4.5 |      | 35<br>40   |      | uA   | 1ms interrupt, no load                         |

| l                | current                                                                | Operating              | 3<br>4.5 |      | 1.0<br>1.1 |      | mA   | 1MHz, no loading                               |

| Іор              |                                                                        | mode                   | 3<br>4.5 |      | 1.2        |      | mA   | 2MHz, no loading                               |

| lil              | Input<br>current                                                       | Weak<br>(1.2M ohms)    | 3<br>4.5 |      | 2.5<br>7.4 |      | uA   | ViI=0v                                         |

| III              | (Internal<br>pull-high)                                                | Strong<br>(100K ohms)  | 3<br>4.5 |      | 30<br>75   |      | uA   | VII-0V                                         |

| loh              | Output high current                                                    |                        | 3<br>4.5 |      | -7<br>-11  |      | mA   | Voh=2.0V<br>Voh=3.5V                           |

|                  | Output low current (Normal current) Output low current (Large current) |                        | 3<br>4.5 |      | 10<br>16   |      | mA   | V <sub>OL</sub> =1.0V<br>V <sub>OL</sub> =1.0V |

| loı              |                                                                        |                        | 3<br>4.5 |      | 20<br>30   |      | mA   | V <sub>OL</sub> =1.0V<br>V <sub>OL</sub> =1.0V |

|                  | PWM output current (Normal)                                            |                        | 3<br>4.5 |      | 60<br>100  |      | mA   | Load=8 ohms                                    |

| I <sub>РWМ</sub> |                                                                        | tput current<br>arge)  | 3<br>4.5 |      | 70<br>117  |      | mA   | Load=8 ohms                                    |

|                  |                                                                        | tput current<br>lltra) | 3<br>4.5 |      | 80<br>134  |      | mA   | Load=8 ohms                                    |

| IDAC             | DAC output current                                                     |                        | 3<br>4.5 |      | 1.4<br>1.6 |      | mA   | Half scale                                     |

| ΔF/F             | Frequency deviation by voltage drop                                    |                        | 3        |      | 1.0        |      | - %  | Fosc(3.0v)-Fosc(2.4v)<br>Fosc(3v)              |

| ۵. /۱            |                                                                        |                        | 4.5      |      | -0.5       |      | ,,,  | Fosc(4.5v)-Fosc(3.0v) Fosc(4.5v)               |

| ΔF/F             | Frequency                                                              | lot deviation          | 3        | -0.5 |            | 0.5  | %    | Fmax(3.0v)-Fmin(3.0v)<br>Fmax(3.0v)            |

| Fosc             | Oscillation Frequency                                                  |                        | -        | 1.99 | 2          | 2.01 | MHz  | VDD=2.0~5.5V                                   |

# **Chapter 2. Hardware Architecture**

### 2.1 Overview

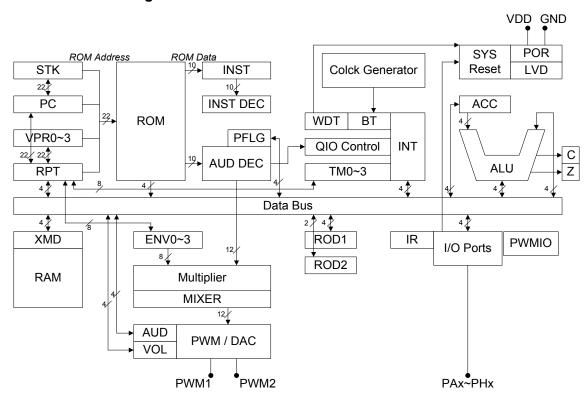

### 2.1.1 Function Block Diagram

### 2.1.2 Hardware Summary Table

| Name       | Function                           | Address         |

|------------|------------------------------------|-----------------|

| STK        | 1-level interrupt dedicated stack  |                 |

| PC         | Program counter                    |                 |

| VPR0~3     | Voice pointer of channel 0~3       |                 |

| RPT        | Multi-function register pointer    | M[0x0~0x4, 0x7] |

| XMD        | Indexed RAM data access register   | M[0x5]          |

| RAM        | 248 nibbles RAM                    |                 |

| ROM        | Program & data ROM                 |                 |

| CHNO       | Active channel select              |                 |

| ENV0~3     | 8-bit Envelope of channel 0~3      |                 |

| DECMD      | PCM / ADPCM control register       | M[0x1CD]        |

| Multiplier | Hardware multiplier for MIDI       |                 |

| MIXER      | Channels audio data mixer          |                 |

| AUD        | Audio output control register      | M[0x1CC]        |

| VOL        | Volume control register            | M[0x1C8]        |

| PWM / DAC  | PWM and D/A converter audio output |                 |

| INST       | Instruction registers              |                 |

| Name            | Function                                 | Address        |

|-----------------|------------------------------------------|----------------|

| INST DEC        | Instruction decoder                      |                |

| PFLG            | Play flag register                       | M[0x1C9]       |

| AUD DEC         | Audio decoder                            |                |

| Clock Generator | Ring oscillator clock generator          |                |

| WDT             | Watch-dog timer and reset generator      |                |

| BT              | System base timer                        |                |

| QIO Control     | Quick-IO control code generator          |                |

| TM0~3           | Sample rate timer of channel 0~3         |                |

| INT             | Interrupt generator                      | M[0x1CB]       |

| ROD1            | ROM[7:4] data access register            | M[0x6]         |

| ROD2            | ROM[9:8] data access register            | M[0x7]         |

| SYS Reset       | System reset generator                   |                |

| POR             | Power reset generator                    |                |

| LVD             | Low voltage detector and reset generator |                |

| ACC             | 4-bit accumulator                        |                |

| ALU             | 4-bit arithmetic logic unit              |                |

| С               | Carry flag for arithmetic                |                |

| Z               | Zero flag for arithmetic                 |                |

| IR              | Infrared transmit block                  |                |

| I/O Ports       | I/O port register                        | M[0x1E0~0x1EF] |

M[]: Memory or System register and the hex number 0x? Between the brackets means its address.

### 2.2 Clock Generator

The clock generator is a Ring oscillator, and users can only select the internal resistor oscillation (INT-R). The INT-R oscillator accuracy is up to  $\pm$  0.5%.

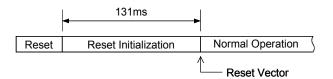

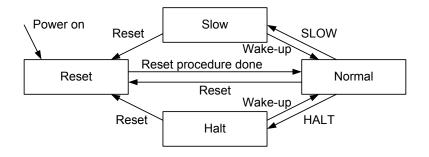

### 2.3 System Reset

Reset Initialization Procedure

11

### 2.3.1 Power-On Reset (POR)

After Power-on, the power-on reset initialization will automatically be set out. After the system leaves the reset initialization procedure, it enters the normal operation and the program counter starts at the reset vector. POR set a POR flag(0x1CB[2]) to high for system low voltage management. It can be cleared by user.

### 2.3.2 Low Voltage Reset (LVR)

When the system enters the normal operation, the power supply voltage must be kept in an effective working voltage range. When the power supply voltage is lower than the effective working voltage range, the system can't work properly. To prevent the system crash, we have a low voltage detector in the NY5+ IC. When the detector detects a harmful low voltage supply, it will cause a low voltage reset. The so-called "low voltage" point of the NY5+ IC is about 1.8v.

### 2.3.3 Watch-Dog Timer Reset (WDTR)

To recover from program malfunction, the NY5+ IC supports an embedded watch-dog timer reset. The WDTR function always works with the program executing. Users have clear the WDT periodically to prevent from timing up with a reset generation. Typically, the minimum time-up period of the WDT is about 15ms. Users can move a 0x5 value to the 0x1CA BTF system register to clear WDT.

### 2.3.4 IO Port External Reset

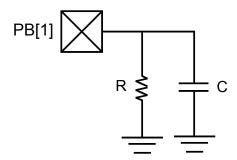

The PX0 (PA0, PB0, PC0, PD0, PE0, PF0, PG0 and PH0) I/O port of the NY5+ can be optioned as a reset pin. A reset pin should always be pulled-high in normal operation, whether users use the built-in internal pull-high resister option or use an external one on PCB with the floating reset option. When the reset pin falls to the ground level, it generates an external reset.

### 2.4 Address Pointer

The NY5+ micro-controller contains a program counter (PC), an interrupt dedicated stack (STK), a multifunction register pointer (RPT) and 4 voice pointers (VPR0~3) for channel 0~3. The length of each address pointer is 22-bit maximum, depends on the product parts. Users have to keep in mind that the initial value of all the pointers is unknown, except the PC.

### 2.4.1 Program Counter (PC)

As a program instruction is executed, the PC will contain the address of the next program instruction to be executed. The PC starts from the reset vector (address 0x000000) after the system reset, and its value is increased by one every instruction cycle unless changed by an interrupt or a branch instruction. The interrupt vector for TOF/QIO is at address 0x000010. The interrupt vector for BT is at address 0x000018.

| Inst./Event | Function                                                                  |

|-------------|---------------------------------------------------------------------------|

| JMP         | Changes the LSB 16-bit of PC, and the reminder MSB bits keep their value. |

| CALL        | Pushes PC+2 to RPT.                                                       |

| RJMP        | Loads RPT to PC, so users can execute a long jump.                        |

| RBPC        | Reads back PC+1 to RPT.                                                   |

| Interrupt   | Pushes PC to STK automatically.                                           |

| Inst./Event | Function                                                                     |

|-------------|------------------------------------------------------------------------------|

| IRET        | Pops STK back to PC. Returns to the main program from the interrupt routine. |

### 2.4.2 Stack (STK)

One level hardware push/pop stack dedicated to the interrupt is available. When an interrupt takes apart, the system pushes the PC to the STK automatically. When the program returns to the main program from the interrupt routine by IRET instruction, the system pops the STK back to the PC.

# 2.4.3 Multi-function Register Pointer (RPT)

As implied in the name, RPT are multi-function registers. Users have to operate RPT in coordination with instructions below.

| Inst./Event | Function                                                |

|-------------|---------------------------------------------------------|

| CALL        | Pushes PC+2 to RPT.                                     |

| RJMP        | Loads RPT to PC.                                        |

| RBPC        | Reads back PC+1 to RPT.                                 |

| LDTM        | Loads RPT[7:0] to TM0~3.                                |

| LDEN        | Loads RPT[7:0] to ENV0~3.                               |

| RBEN        | Reads back ENV0~3 to RPT[7:0].                          |

| PLAY        | Loads RPT to VPR0~3.                                    |

| RBVPR       | Reads back VPR0~3 to RPT.                               |

| RBRO        | Use RPT as address to read ROM data.                    |

| XMD         | Use {RPT3, RPT2} as address to access indexed RAM data. |

### 2.4.4 Voice Pointer (VPR)

Because NY5+ is a 4-channel sound processor, 4 voice pointers are necessary for playing speech or MIDI of each channel. When PLAY is executed, the system loads RPT to VPR of the channel which assigned by the CH# register. So users have to move the start address of the speech or MIDI data to RPT first. Besides, users can read VPR back by RBVPR instruction, because RBVPR moves VPR of the channel which assigned by the CH# register to RPT.

### 2.5 Arithmetic Logic Unit (ALU)

The NY5+ series provides a 4-bit arithmetic logic unit with a 4-bit accumulator to perform logic, unsigned arithmetic, data transfer and conditional branch operation. We have two flags (carry and zero) to indicate the result of the operation. One or two operands will be the data sources of the ALU operation. The operands can be ACC, RAM, register, or literal constant data.

### 2.5.1 ALU Instruction Summary

### 2.5.1.1 Logic Instruction

| Instruction | Function                     | Flag Influenced |

|-------------|------------------------------|-----------------|

| XORA m      | $A \leftarrow M[m] \oplus A$ | Z               |

| ANDA m      | A ← M[m] & A                 | Z               |

| ORA m       | A ← M[m]   A                 | Z               |

| XORL L      | $A \leftarrow A \oplus L$    | Z               |

| ANDL L      | A ← A & L                    | Z               |

| ORL L       | A ← A   L                    | Z               |

### 2.5.1.2 Arithmetic Instruction

| Instruction | Function                    | Flag Influenced |

|-------------|-----------------------------|-----------------|

| INCM m      | M[m] ← M[m] + 1             | C, Z            |

| DECM m      | M[m] ← M[m] - 1             | C, Z            |

| ADDA m      | $A \leftarrow A + M[m] + C$ | C, Z            |

| ADDL L      | $A \leftarrow A + L + C$    | C, Z            |

| INCA        | A ← A + 1                   | C, Z            |

| DECA        | A ← A - 1                   | C, Z            |

### 2.5.1.3 Data Transfer Instruction

| Instruction | Function               | Flag Influenced |

|-------------|------------------------|-----------------|

| MVAM        | $M[m] \leftarrow A$    |                 |

| MVMA        | $A \leftarrow M[m]$    | Z               |

| MVRM        | $M[m] \leftarrow R[r]$ |                 |

| MVMR        | $R[r] \leftarrow M[m]$ |                 |

| MVLA        | $A \leftarrow L$       |                 |

| RSTC        | C ← 0                  | С               |

| SETC        | C ← 1                  | С               |

The width of the memory register address `r' of MVRM and MVMR command is 2-bit, and the MSB of the memory register is forced to be 1. So users can only use the three commands to handle RPT0~3. The width of the RAM or memory register address `m' of MVRM, and MVMR command is 4-bit, and

the MSB 2-bit of the address is forced to be 0x3. Users can only use the two instructions to handle RAM or memory register of address 0x30~0x3F, but the RAM page is still working.

### 2.5.1.4 Conditional Branch Instruction

| Instruction | Function          | Flag Influenced |

|-------------|-------------------|-----------------|

| SANL        | Skip if A != L    |                 |

| CPAB        | Skip if (A & L)=0 |                 |

| SCEZ(CPCZ)  | Skip if C = 0     |                 |

| SZEZ(CPZZ)  | Skip if Z = 0     |                 |

A conditional branch instruction compares two data and skips next instruction if they are equal. The skip operation is making an instruction NOP, not jump across it.

$\oplus$  : Exclusive OR bitwise logical operation

&: AND bitwise logical operation

|: OR bitwise logical operation

A: 4-bit Accumulator data

C: 1-bit carry flag data

L: 4-bit immediately literal data

M[m]: 4-bit RAM or memory register data at memory address m

R[r]: 4-bit memory register data at register address r

Z: 1-bit zero flag data

### 2.5.2 ALU Related Status Flag

| Symbol | Flag         | Description                                              |

|--------|--------------|----------------------------------------------------------|

| C      | C Carry flag | C=1 if a carry-out occurs after an addition operation.   |

| C      |              | C=0 if a borrow-in occurs after a subtraction operation. |

| Z      | Zero flag    | Z=1 if the result of an ALU operation is zero.           |

Besides RSTC and SETC commands directly assign the value of the carry flag, C is influenced by the arithmetic result. C means carry and also means the complement of borrow. If the addition operation is larger than 0xF, C=1, and C=0 if the result  $\leq$ 15. If the subtraction operation is smaller than 0, C=0, and C=1 if the result  $\geq$ 0.

### 2.6 Memory Organization

There are maximum 4M words ROM, 248 nibbles of RAM and some dedicated system control register. The registers are divided into normal system registers and 8 nibbles of Multi-function registers.

### 2.6.1 ROM

A large program/data/voice single ROM is provided, and its structure is shown below. The reserved region contains system information and can't be utilized by users. The program page is limited by the unconditional branch instruction: JMP and CALL. Because it can only handle 16-bit length address of ROM, the program page size is 64K words.

| Address  | ROM Map                                |

|----------|----------------------------------------|

| 0x000000 | Reset Vector                           |

| 0x00000F |                                        |

| 0x000010 | Interrupt Vector for TOF/QIO           |

| 0x000017 |                                        |

| 0x000018 | Interrupt Vector for BT                |

| 0x00001E |                                        |

| 0x00001F |                                        |

|          | Reserved                               |

| 0x0009FF |                                        |

| 0x000A00 |                                        |

|          | Program & Data Space<br>Program Page 0 |

| 0x00FFFF |                                        |

| 0x010000 |                                        |

|          | Program & Data Space                   |

|          |                                        |

### 2.6.2 RAM

NY5+ provide 248 nibbles RAM space. The address for RAM is 0x008~0x0FF. The first space from 0x08 to 0x3F is function RAM space, it only needs one-word instruction operation. And the second space from 0x040 to 0x0FF is data RAM space; the related operation is two-word instruction.

In addition to the immediate addressing mode, the indexed addressing mode is also supported. The page and address of the indexed RAM should be stored into RPT3 and RPT2 first, and users can read from or write in the XMD memory register to realize the indexed RAM access.

| Address | RAM map                   |

|---------|---------------------------|

| 0x000   |                           |

|         | Memory Register           |

| 0x007   |                           |

| 800x0   | 50 wilhble Franchism DAM  |

| 0x03F   | 56 nibble Function RAM    |

| 0x03F   |                           |

| 0.040   | 192 nibble Function RAM   |

| 0x0FF   | TOZ TIBOTO T GITOGOTT WIN |

| 0x100   |                           |

|         | Reserved                  |

| 0x1C7   |                           |

| 0x1C8   |                           |

| 0.405   | System registers          |

| 0x1CF   |                           |

| 0x1D0   | Reserved                  |

| 0x1DF   | Treserved                 |

| 0x1E0   |                           |

|         | System registers          |

| 0x1EF   | , -                       |

| 0x1F0   |                           |

|         | Reserved                  |

| 0x1F3   |                           |

| 0x1F4   | System registers          |

| 0x1FF   | System registers          |

| 0.7111  |                           |

### 2.6.3 Memory Register

8 nibbles of memory register share the address with RAM. The page number of RAM has no relationship with the memory register address.

| Address | Name | Description                                 |

|---------|------|---------------------------------------------|

| 0       | RPT0 | Multi-function register pointer bit [3:0]   |

| 1       | RPT1 | Multi-function register pointer bit [7:4]   |

| 2       | RPT2 | Multi-function register pointer bit [11:8]  |

| 3       | RPT3 | Multi-function register pointer bit [15:12] |

| Address | Name | Description                                 |

|---------|------|---------------------------------------------|

| 4       | RPT4 | Multi-function register pointer bit [19:16] |

| 5       | XMD  | Indexed RAM data access register            |

| 6       | ROD1 | ROM data bit [7:4] access register          |

| 7       | RPT5 | Multi-function register pointer bit [21:20] |

| /       | ROD2 | ROM data bit [9:8] access register          |

# 2.6.4 System Register

The NY5+ series provides only two instructions to access the system registers.

| Address | Name | Description                         |

|---------|------|-------------------------------------|

| 1C8     | VOL  | 16-level Volume control register    |

| 1C9     | PFLG | Play flag register                  |

| 1CA     | BTF  | Interrupt flag control register     |

| 1CB     | BTC  | Interrupt control register          |

| 1CC     | AUD  | Audio output control register       |

| 1CD     | CHMD | Channel control register            |

| 1CE     | RBDA | MSB 4 bits of the data after Mixer  |

| 1CF     | LVD  | Low Voltage Detect control register |

| Address | Name | Description           |

|---------|------|-----------------------|

| 1E0     | PA   | PA control register   |

| 1E1     | PAIO | PAIO control register |

| 1E2     | PB   | PB control register   |

| 1E3     | PBIO | PBIO control register |

| 1E4     | PC   | PC control register   |

| 1E5     | PCIO | PCIO control register |

| 1E6     | PD   | PD control register   |

| 1E7     | PDIO | PDIO control register |

| 1E8     | PE   | PE control register   |

| 1E9     | PEIO | PEIO control register |

| 1EA     | PF   | PF control register   |

| 1EB     | PFIO | PFIO control register |

| 1EC     | PG   | PG control register   |

| 1ED     | PGIO | PGIO control register |

| 1EE     | PH   | PH control register   |

| 1EF     | PHIO | PHIO control register |

| Address | Name       | Description                        |

|---------|------------|------------------------------------|

| 1F4     | PCHNO      | PWM-IO CH# control register        |

| 1F5     | Frame Rate | PWM-IO Frame Rate control register |

| 1F6     | Step       | PWM-IO Step control register       |

| Address | Name     | Description                              |

|---------|----------|------------------------------------------|

| 1F7     | EN       | PWM-IO Enable control register           |

| 1F8     | B0_DutyL | Bit-0 Low nibbles Duty control register  |

| 1F9     | B0_DutyH | Bit-0 High nibbles Duty control register |

| 1FA     | B1_DutyL | Bit-1 Low nibbles Duty control register  |

| 1FB     | B1_DutyH | Bit-1 High nibbles Duty control register |

| 1FC     | B2_DutyL | Bit-2 Low nibbles Duty control register  |

| 1FD     | B2_DutyH | Bit-2 High nibbles Duty control register |

| 1FE     | B3_DutyL | Bit-3 Low nibbles Duty control register  |

| 1FF     | B3_DutyH | Bit-3 High nibbles Duty control register |

### 2.6.5 Register without Memory Allocation

| Name  | Description                                      | Instruction |

|-------|--------------------------------------------------|-------------|

| CH#   | 2-bit channel number register of working channel | CHNO        |

| TCS   | 2-bit timer clock source register of CH#         | CHTCS       |

| TM    | 8-bit sample rate timer of CH#                   | LDTM        |

| ENIV/ | 9 hit anyolong of CLI#                           | LDEN        |

| ENV   | 8-bit envelope of CH#                            | RBEN        |

### 2.7 IO Ports

There are at most 32 I/O pins, designated as PAx through PHx, and x=0~3. All the I/O pins are bi-directional. An individual and independent register bit can determine the direction of each I/O pin. These register bits are PAIO (\$1E1), PBIO (\$1E3), PCIO (\$1E5), PDIO (\$1E7), PEIO (\$1E9), PFIO (\$1EB), PGIO (\$1ED) and PHIO (\$1EF).

Using as input pin of each I/O, there are 3 kinds of mask option. Users can select input with pull-high resistor, input without pull-high resistor, or input with register-controlled pull-high resistor (high-to-low wakeup only). If users want to enable/disable pull-high resistor by register during program execution, only high-to-low level change on this pin can wakeup NY5+. On the other hand, if the pull-high resistor is fixed by option, either high-to-low or low-to-high level change on this pin can wakeup NY5+. Users can refer Chapter 3.14 I/O Ports Register for details.

The pull-high resistor of all the I/O pins has two kinds of option: weak and strong. The weak one is about  $1.2M\Omega@3V$  for normal application and the strong one is about  $100K\Omega@3V$  usually for key matrix function. When users decide this option, the same strength of pull-high resistor will be applied to all I/O pin.

Using as output pin of each I/O, there are 3 kinds of mask option. Users can select output with normal drive current and normal sink current or normal drive current and large sink current.

The PX0 port means the PA0, PB0, PC0, PD0, PE0, PF0, PG0 or PH0 port can also be optioned as an external reset pin or an infrared (IR) output pin. A reset port can possess a pull-high resister or not, and an IR port can be initial low or high and also large sink current or not.

| Category                 | Option                      | Description                           |  |  |

|--------------------------|-----------------------------|---------------------------------------|--|--|

|                          | Config as IR output         |                                       |  |  |

| PA0<br>PC0<br>PE0<br>PG0 | Config as RESET input       | choose 1 of 3                         |  |  |

|                          | Config as normal IO         |                                       |  |  |

|                          | Config Pull-high            | Disable / Enable                      |  |  |

| 1 00                     | Config large sink current   | Disable / Enable                      |  |  |

|                          | Config PX register          | wakeup status /<br>pull-high/floating |  |  |

| PA1~3                    | Config Pull-high            | Disable / Enable                      |  |  |

| PC1~3                    | Config large sink current   | Disable / Enable                      |  |  |

| PE1~3<br>PG1~3           | Config PX register          | wakeup status /<br>pull-high/floating |  |  |

|                          | Config as IR output         |                                       |  |  |

|                          | Config as RESET input       |                                       |  |  |

| PB0                      | Config as PWM-IO output     | choose 1 of 4                         |  |  |

| PD0                      | Config as normal IO         |                                       |  |  |

| PF0<br>PH0               | Config Pull-high            | Disable / Enable                      |  |  |

|                          | Config large sink current   | Disable / Enable                      |  |  |

|                          | Config PX register          | wakeup status /<br>pull-high/floating |  |  |

| PB1~3                    | Config Pull-high            | Disable / Enable                      |  |  |

| PD1~3<br>PF1~3           | Config large sink current   | Disable / Enable                      |  |  |

| PH1~3<br>PH1~3           | Config PX register          | wakeup status /<br>pull-high/floating |  |  |

| All I/O                  | I/O port pull-high resister | Weak/ Strong                          |  |  |

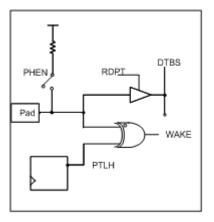

# 2.7.1 Pull-High Input Mode

**Pull-high Input Mode Configuration**

Pad status of PA~PH, which are set as input mode, can be read in by MVMA. If the pads are not connected, an internal pull-high resistor will be optioned to pull the pad toward supply voltage. All I/O pins set as input mode can be used to wake-up the system, and the wake-up procedure will be launched if the comparison between PTLH and pad status is unmatched. Therefore, users have to store the current pad status into PTLH before entering Halt or Slow mode. The system will be waked-up when pad voltage change is detected.

### 2.7.2 Floating Input Mode

It is similar to the pull-high input mode except the internal pull-high resistor is not connected. User should apply external pull-high resistor or pull-low resistor for high-resistance switch applications.

### 2.7.3 Output Mode

**Output Mode Configuration**

User can select output mode to supply both normal drive current and normal/large sink current by setting related mask options. But drive current of NY5+ is always weaker than normal sink current, about half the scale.

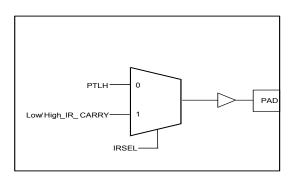

### 2.8 Infrared Transmitter

The NY5+ series provides an infrared transmit block which is used to send infrared signal. Users can option a PX[0] (PA0, PB0, PC0, PD0, PE0, PF0, PG0, or PH0) IO as an IR output. Users can option both the IR carrier frequency and IR Low/High carrier. The IR Low/High carrier means that if users option the IR Low carrier, the IR output port sends infrared signal when the IO port register value is low, and vice versa.

| Category | Option              | Description     |  |

|----------|---------------------|-----------------|--|

|          | IR frequency        | 38.46~55.56 KHz |  |

| IR       | ID law/high agging  | Low             |  |

|          | IR low/high carrier | High            |  |

### 2.9 PWM-IO Generator

The NY5+ has 4 sets of PWM-IO groups - PB/ PD/ PF/ PH, each with four PWM outputs (PB0~PB3, PD0~PD3, PF0~PF3 and PH0~PH3). Each four PWM outputs share a PWM 8-bit timer, every PWM output has its own duty and output port.

Four PWM outputs share a timer

Programmable divider of timer clock

8-bit counter for each timer

8-bit PWM duty

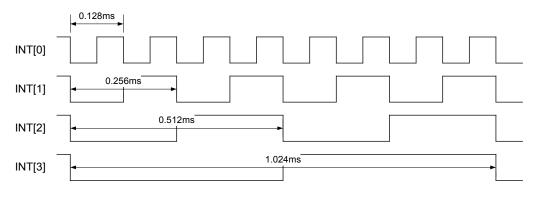

### 2.10 Interrupt Generator

There is one hardware interrupt and it has 3 different sources in NY5+. The interrupt event can be a fixed interval of the system base timer (BT), the timer overflow flag (TOF), or the quick-IO flag (QIOF). The TOF can be selected as one of the sample rate timer overflow by the register INT, and the QIOF arises as a QIO control code of any channel coming up. There is a system base timer in the NY5+ IC, which functions as long as the IC isn't in the halt mode. We provide 4 fixed intervals from the system base timer for interrupt source: 0.128, 0.256, 0.512 and 1.024ms.

As an interrupt occurs, NY5+ stores the accumulator (ACC), carry flag (C), zero flag (Z) and RAM page (PG) automatically. Then move PC to STK, and jump to the interrupt vector (0x000010 or 0x000018). An interrupt routine finishes with an IRET instruction. The IC draws the ACC, C, Z and PG back, and moves STK to PC back to jump back the main program.

The interrupt event of BT will be automatically cleared after entering the interrupt routine, but the TOF and QIOF have to be cleared by users.

## 2.11 Audio Synthesizer Structure

There are 4-ch speech or MIDI audio output, and all modes are auto-played back by hardware. Different channel mode possesses different hardware structure. It provides a hardware mixer to mix the channel data. Two audio output stages: DAC and PWM are supported. Please noticed that 2MHz is required for over 2-ch speech or MIDI.

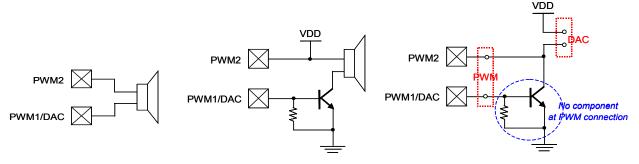

### 2.11.1 Audio Output

By set the AUD register, PWM or DAC can be easily chosen as the audio output stage. Besides, it provides a pad detecting mechanism. The pad detecting mechanism detects the PWM2 pad during the reset initialization period, and sets the initial value of the audio output register as PWM if the PWM2 connection is floating, or sets the initial value of the audio output register as DAC if the PWM2

connection is high. In conclusion, connect the speaker to PWM1 and PWM2 only if using PWM, otherwise connect PWM2 to VDD if using DAC. Since the mechanism sets only the initial value of AUD, don't change the value of the AUD register if the pad detecting mechanism is adopted.

| PWM2 Pad           | Audio Output Initialization |

|--------------------|-----------------------------|

| Speaker (Floating) | PWM                         |

| VDD                | DAC                         |

**PWM Output Connection**

DAC Output Connection

PWM/DAC Connection Together

When using the PWM output, we provide an option of normal PWM current, large PWM current or ultra PWM current for different customer demand. The ultra PWM current consumes more current and makes sound louder.

### 2.11.2 Volume Control

Both PWM and DAC supports 16 steps hardware volume control by the VOL register, 0x0~0xF.

### 2.12 Low Voltage Detector (LVD)

There is one hardware voltage detector in NY5+. It offers four levels for various application, 2.0v, 2.2v, 2.4v, 2.8v, 3.0v, 3.3v and 3.6v controlled by register \$LVD. The voltage detection function has to be enabled first, then select specific level for application, the flag will go to high while VDD is lower than selected level. User can check power status by setting different level and monitoring the flag.

Since VDD voltage is fixed on ICE system, so the LVD result is always same. Also for NY5+\_FDB (both 4Mb & 16Mb), the lowest 3 levels 2.0v, 2.2v, and 2.4v cannot be detected due to Flash memory voltage limitation on PCB. Please verify LVD function on OTP chips.

# **Chapter 3. System Control**

### 3.1 Introduction

The VOL, PFLG, AUD, CH#, TCS0~3, TM0~3 and ENV0~3 are audio control related registers. The PA~H are I/O ports registers. INT register is used to control or access the system base timer (BT) the interrupt (INT), timer overflow flag (TOF), quick-IO flag (QIOF) and watch dog timer (WDT). The combination of RPT0~5 are multi-function register pointer. The C and Z are arithmetic associated flags. The PG and XMD are RAM access registers. The ROD1 and ROD2 registers are used to read the ROM data.

### 3.1.1 System Register Address Map

| Addr     | Name  | R/W | Bit   | Data                   | Description                             | Initial             | Wake-up               |     |     |     |     |     |     |  |  |       |    |                     |          |

|----------|-------|-----|-------|------------------------|-----------------------------------------|---------------------|-----------------------|-----|-----|-----|-----|-----|-----|--|--|-------|----|---------------------|----------|

| 1C8      | VOL   | R/W | [3:0] |                        | 16- level volume control                | 0x4                 | U                     |     |     |     |     |     |     |  |  |       |    |                     |          |

| 1C9 PFLG | R     | [0] | 0/1   | Play Flag of Channel 0 |                                         |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          | R     | [1] | 0/1   | Play Flag of Channel 1 | 0.40                                    |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          | R     | [2] | 0/1   | Play Flag of Channel 2 | 0x0                                     | U                   |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          | R     | [3] | 0/1   | Play Flag of Channel 3 |                                         |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       |     | [0]   | 0/1                    | System base timer 0.128ms               | Х                   | Х                     |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       |     | [1]   | 0/1                    | System base timer 0.256ms               | Х                   | Х                     |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | R   | [2]   | 0/1                    | System base timer 0.512ms               | Х                   | Х                     |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       |     | [3]   | 0/1                    | System base timer 1.024ms               | Х                   | Х                     |     |     |     |     |     |     |  |  |       |    |                     |          |

| 1CA      | BTF   | W   | [3:0] | 0101                   | Clear WDT                               | Clear               | U                     |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | W   | [3:0] | 1000                   | TOF = Timer 0 overflow                  |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | W   | [3:0] | 1001                   | TOF = Timer 1 overflow                  | Ti 0                |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | W   | [3:0] | 1010                   | TOF = Timer 2 overflow                  | Timer 0             | U                     |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | W   | [3:0] | 1011                   | TOF = Timer 3 overflow                  |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       |     |       |                        |                                         | 00                  | Interrupt ~= 0.125 ms |     |     |     |     |     |     |  |  |       |    |                     |          |

|          | R/V   | DAM | [4.0] | 01                     | Interrupt ~= 0.25 ms                    | 0.405               |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

| 400      |       | DTO | втс   | DTO                    | DTC                                     | DTO                 | DTO                   | DTO | DTO | DTO | DTO | DTC | DTC |  |  | [1:0] | 10 | Interrupt ~= 0.5 ms | 0.125 ms |

| 1CB      | BIC   | BIC | ВІС   |                        | 11                                      | Interrupt ~= 1.0 ms |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | R/W | [2]   | 0/1                    | POR Flag                                |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | R/W | [3]   | 0/1                    | BT interrupt Disable / Enable           |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | R/W | [0]   | 0/1                    | QIO flag, write 0 to clear flag         |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

| 100      | ALID  | R/W | [1]   | 0/1                    | TOF flag, write 0 to clear flag         |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

| 1CC      | AUD   | R/W | [2]   | 0/1                    | Audio Output Disable / Enable           |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | R/W | [3]   | 0/1                    | Audio output = Current DAC / PWM output |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | R/W | [0]   | 0/1                    | QIO interrupt Disable / Enable          |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

| 100      | CLIMP | R/W | [1]   | 0/1                    | TOF interrupt Disable / Enable          |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

| 1CD      | CHMD  | R/W | [2]   | 0/1                    | Reserved                                |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

|          |       | R/W | [3]   | 0/1                    | Tail Disable / Enable                   |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

| 1CE      | RBDA  | R   | [3:0] | 0/1                    | MSB 4 bits of the data after Mixer      |                     |                       |     |     |     |     |     |     |  |  |       |    |                     |          |

| 1CF      | LVD   | R/W | [2:0] | 000                    | Voltage Detect function disable/enable  | U                   | U                     |     |     |     |     |     |     |  |  |       |    |                     |          |

| Addr        | Name | R/W  | Bit   | Data  | Description                                                                                                                        | Initial                                                                  | Wake-up |  |

|-------------|------|------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------|--|

|             |      |      |       | 001   | Check Power < 2.0v => Flag = High                                                                                                  |                                                                          |         |  |

|             |      |      |       | 010   | Check Power < 2.2v => Flag = High                                                                                                  |                                                                          |         |  |

|             |      |      |       | 011   | Check Power < 2.4v => Flag = High                                                                                                  |                                                                          |         |  |

|             |      |      |       | 100   | Check Power < 2.8v => Flag = High                                                                                                  |                                                                          |         |  |

|             |      |      |       | 101   | Check Power < 3.0v => Flag = High                                                                                                  |                                                                          |         |  |

|             |      |      |       | 110   | Check Power < 3.3v => Flag = High                                                                                                  |                                                                          |         |  |

|             |      |      |       | 111   | Check Power < 3.6v => Flag = High                                                                                                  |                                                                          |         |  |

|             |      | R    | [3]   | 0/1   | LVD Flag, disable to Low                                                                                                           |                                                                          |         |  |

| 1D0~<br>1DF |      | R/W  | [3:0] |       | Reserved                                                                                                                           |                                                                          |         |  |

|             |      | _    | [0.0] | 0/4   | PxIO = 1: Read input pad data                                                                                                      |                                                                          |         |  |

| . — -       |      | R    | [3:0] | 0/1   | PxIO = 0: Read output register                                                                                                     |                                                                          |         |  |

| 1E0         | PA   | W    | [3:0] | 0/1   | PxIO = 1: Wake-up status (Option Disable) PxIO = 1: Floating / Pull-high (Option Enable) PxIO = 0: Write to port A output register |                                                                          |         |  |

| 1E1         | PAIO | R/W  | [3:0] | 0/1   | Port X direction = Output / Input                                                                                                  |                                                                          |         |  |

|             | 1710 | 1000 | [0.0] | 0/1   | PxIO = 1: Read input pad data                                                                                                      |                                                                          |         |  |

|             |      | R    | [3:0] | 0/1   | PxIO = 0: Read output register                                                                                                     |                                                                          |         |  |

| 1E2         | РВ   |      |       |       | PxIO = 1: Wake-up status (Option Disable)                                                                                          |                                                                          |         |  |

|             |      | W    | [3:0] | 0/1   | PxIO = 1: Floating / Pull-high (Option Enable)                                                                                     |                                                                          |         |  |

|             |      |      |       |       | PxIO = 0: Write to port A output register                                                                                          |                                                                          |         |  |

| 1E3         | PBIO | R/W  | [3:0] | 0/1   | Port X direction = Output / Input                                                                                                  |                                                                          |         |  |

|             |      | R    | R     | [3:0] | 0/1                                                                                                                                | PxIO = 1: Read input pad data                                            |         |  |

| 1E4         | PC   | W    | W     |       |                                                                                                                                    | PxIO = 0: Read output register PxIO = 1: Wake-up status (Option Disable) |         |  |

|             |      |      |       | [3:0] | 0/1                                                                                                                                | PxIO = 1: Floating / Pull-high (Option Enable)                           |         |  |

|             |      |      |       |       | PxIO = 0: Write to port A output register                                                                                          |                                                                          |         |  |

| 1E5         | PCIO | R/W  | [3:0] | 0/1   | Port X direction = Output / Input                                                                                                  |                                                                          |         |  |

|             |      | R    | [3:0] | 0/1   | PxIO = 1: Read input pad data                                                                                                      |                                                                          |         |  |

| 1E6         | PD   |      | [0.0] | 0, 1  | PxIO = 0: Read output register                                                                                                     |                                                                          |         |  |

| 120         | 10   | W    | [3:0] | 0/1   | PxIO = 1: Wake-up status (Option Disable) PxIO = 1: Floating / Pull-high (Option Enable)                                           |                                                                          |         |  |

|             |      | "    | V V   | [0.0] | 0/1                                                                                                                                | PxIO = 0: Write to port A output register                                |         |  |

| 1E7         | PDIO | R/W  | [3:0] | 0/1   | Port X direction = Output / Input                                                                                                  |                                                                          |         |  |

|             |      | В    | 10.01 | 0/1   | PxIO = 1: Read input pad data                                                                                                      |                                                                          |         |  |

| 450         |      | R    | [3:0] | 0/1   | PxIO = 0: Read output register                                                                                                     |                                                                          |         |  |

| 1E8         | PE   |      |       |       | PxIO = 1: Wake-up status (Option Disable) PxIO = 1: Floating / Pull-high (Option Enable)                                           |                                                                          |         |  |

|             |      | W    | [3:0] | 0/1   | PxIO = 0: Write to port A output register                                                                                          |                                                                          |         |  |

| 1E9         | PEIO | R/W  | [3:0] | 0/1   | Port X direction = Output / Input                                                                                                  |                                                                          |         |  |

|             |      |      |       | _     | PxIO = 1: Read input pad data                                                                                                      |                                                                          |         |  |

|             |      | R    | [3:0] | 0/1   | PxIO = 0: Read output register                                                                                                     |                                                                          |         |  |

| 1EA         | PF   |      |       |       | PxIO = 1: Wake-up status (Option Disable)                                                                                          |                                                                          |         |  |

|             |      | W    | [3:0] | 0/1   | PxIO = 1: Floating / Pull-high (Option Enable) PxIO = 0: Write to port A output register                                           |                                                                          |         |  |

| 1EB         | PFIO | R/W  | [3:0] | 0/1   | Port X direction = Output / Input                                                                                                  |                                                                          |         |  |

| 1EC         | PG   | R    | [3:0] | 0/1   | PxIO = 1: Read input pad data                                                                                                      |                                                                          |         |  |

| 'LO         | 1 0  | 1    | [٥.٥] | 0/1   | 1 Alo - 1. Nead input pad data                                                                                                     |                                                                          |         |  |

| Addr            | Name            | R/W         | Bit     | Data    | Description                                                                              | Initial         | Wake-up |         |          |     |     |     |                                  |  |  |

|-----------------|-----------------|-------------|---------|---------|------------------------------------------------------------------------------------------|-----------------|---------|---------|----------|-----|-----|-----|----------------------------------|--|--|

|                 |                 |             |         |         | PxIO = 0: Read output register                                                           |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 | \\\         |         |         | PxIO = 1: Wake-up status (Option Disable) PxIO = 1: Floating / Pull-high (Option Enable) |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 | W           | [3:0]   | 0/1     | PxIO = 0: Write to port A output register                                                |                 |         |         |          |     |     |     |                                  |  |  |

| 1ED             | PGIO            | R/W         | [3:0]   | 0/1     | Port X direction = Output / Input                                                        |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 |             |         |         | PxIO = 1: Read input pad data                                                            |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 | R           | [3:0]   | 0/1     | PxIO = 0: Read output register                                                           |                 |         |         |          |     |     |     |                                  |  |  |

| 1EE             | PH              | W           | [3:0]   | 0/1     | PxIO = 1: Wake-up status (Option Disable) PxIO = 1: Floating / Pull-high (Option Enable) |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 |             |         |         | PxIO = 0: Write to port A output register                                                |                 |         |         |          |     |     |     |                                  |  |  |

| 1EF             | PHIO            | R/W         | [3:0]   | 0/1     | Port X direction = Output / Input                                                        |                 |         |         |          |     |     |     |                                  |  |  |

| 1F0<br>~<br>1F3 |                 | R/W         | [3:0]   |         | Reserved                                                                                 |                 |         |         |          |     |     |     |                                  |  |  |

| 454             | PWM-IO          | DAM         | [1:0]   |         | PCH# = 0, 1, 2. 3                                                                        |                 |         |         |          |     |     |     |                                  |  |  |

| 1F4             | CHNO            | R/W         | [3:2]   |         | Reserved                                                                                 |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 |             |         | 00      | Frame Rate = 128us / 16us(2M)                                                            |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 | - 1 12////  | [4.0]   | 01      | Frame Rate = 512us / 64us (500K)                                                         |                 |         |         |          |     |     |     |                                  |  |  |

| 1F5             | PWM-IO<br>FRate |             | [1:0]   | 10      | Frame Rate = 2ms / 256us(125K)                                                           |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 |             |         | 11      | Frame Rate = 16ms / 2ms(15.625K)                                                         |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 |             |         |         |                                                                                          |                 | [3:2]   |         | Reserved |     |     |     |                                  |  |  |

|                 |                 | R/W         | [0]     | 0/1     | Px[0] 256step(8-b) / 32step(5-b)                                                         |                 |         |         |          |     |     |     |                                  |  |  |

| 1F6             | PWM-IO          | R/W         | [1]     | 0/1     | Px[1] 256step(8-b) / 32step(5-b)                                                         |                 |         |         |          |     |     |     |                                  |  |  |

| 11-0            | Px_Step         | Px_Step     | Px_Step | Px_Step | Px_Step                                                                                  | Px_Step         | Px_Step | Px_Step | Px_Step  | R/W | [2] | 0/1 | Px[2] 256step(8-b) / 32step(5-b) |  |  |

|                 |                 | R/W         | [3]     | 0/1     | Px[3] 256step(8-b) / 32step(5-b)                                                         |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 | R/W         | [0]     | 0/1     | Px[0] Dis/En                                                                             |                 |         |         |          |     |     |     |                                  |  |  |

| 1F7             | PWM-IO          | R/W         | [1]     | 0/1     | Px[1] Dis/En                                                                             |                 |         |         |          |     |     |     |                                  |  |  |

| 11 7            | Px_Enable       | R/W         | [2]     | 0/1     | Px[2] Dis/En                                                                             |                 |         |         |          |     |     |     |                                  |  |  |

|                 |                 | R/W         | [3]     | 0/1     | Px[3] Dis/En                                                                             |                 |         |         |          |     |     |     |                                  |  |  |

| 1F8             | Px[0]_Duty      | R/W         | [3:0]   |         | Px[0]_Duty[3:0]                                                                          |                 |         |         |          |     |     |     |                                  |  |  |

| 1F9             | i x[o]_buty     | R/W         | [3:0]   |         | Px[0]_Duty[7:4]                                                                          |                 |         |         |          |     |     |     |                                  |  |  |

| 1FA             | Px[1]_Duty      | R/W         | [3:0]   |         | Px[1]_Duty[3:0]                                                                          |                 |         |         |          |     |     |     |                                  |  |  |

| 1FB             |                 | R/W         | [3:0]   |         | Px[1]_Duty[7:4]                                                                          |                 |         |         |          |     |     |     |                                  |  |  |

| 1FC             | Px[2]_Duty      | R/W         | [3:0]   |         | Px[2]_Duty[3:0]                                                                          |                 |         |         |          |     |     |     |                                  |  |  |

| 1FD             | i vizi_Duty     | R/W         | [3:0]   |         | Px[2]_Duty[7:4]                                                                          |                 |         |         |          |     |     |     |                                  |  |  |

| 1FE             | Px[3]_Duty      | R/W         | [3:0]   |         | Px[3]_Duty[3:0]                                                                          |                 |         |         |          |     |     |     |                                  |  |  |

| 1FF             | r x[3]_Duty     | i v[o]_Duty | R/W     | [3:0]   |                                                                                          | Px[3]_Duty[7:4] |         |         |          |     |     |     |                                  |  |  |

# 3.1.2 Memory Register Address Map

| Addr | Name | R/W | Bit   | Description                             | Initial | Wake-up |

|------|------|-----|-------|-----------------------------------------|---------|---------|

| 0    | RPT0 | R/W | [3:0] | Multi-function register pointer [3:0]   | Х       | U       |

| 1    | RPT1 | R/W | [3:0] | Multi-function register pointer [7:4]   | Х       | U       |

| 2    | RPT2 | R/W | [3:0] | Multi-function register pointer [11:8]  | Х       | U       |

| 3    | RPT3 | R/W | [3:0] | Multi-function register pointer [15:12] | Х       | U       |

| 4    | RPT4 | R/W | [3:0] | Multi-function register pointer [19:16] | X       | U       |

| Addr | Name | R/W | Bit   | Description                             | Initial | Wake-up |

|------|------|-----|-------|-----------------------------------------|---------|---------|

| 5    | XMD  | R/W | [3:0] | Indexed RAM data access register        | Х       | Х       |